|

| ALTERA EPM7128STC100-15 CPLDによるCRTC | 2002.06.02 (最終更新2004.01.13) |

|

|

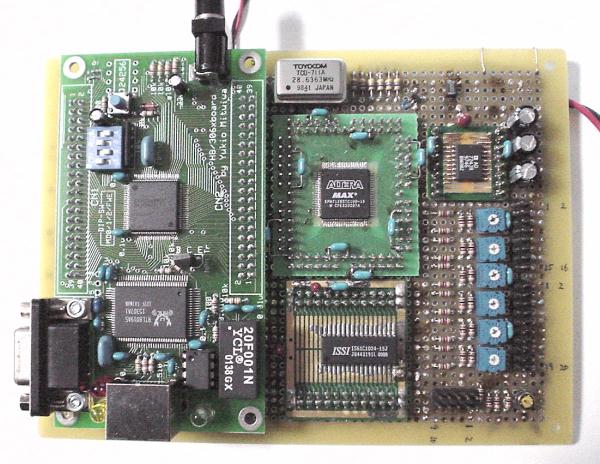

ALTERA EPM7128STC100-15 CPLDを使ってCRTC(CRTコントローラ)を作ってみました。 このたぐいの物はCRTコントローラの他にディスプレイコントローラとかビデオコントローラとか グラフィックコントローラとか呼び方はいろいろあるようですがその区別についてはよく知りません。 今回の物は秋月電子通商で販売されているSHARP製液晶モジュールLM32C041にも対応しているので 一種のLCDC(LCDコントローラ)も兼ねているとも言えるかも知れません。 ここで使用したCPLDは128マクロセル(2500ユーザブルゲート)、84ユーザIOピン、ピン間遅延15nsの もので、XilinxならXC95108とXC95144の中間程度の規模に相当するデバイスです。 何故XilinxでなくALTERAかというと主に個人的な趣味です。入手の都合もありましたが。 製作したCRTCの表示仕様は以下の4通りです。 基板上の回路自体は同一で、どの仕様にするかはCPLDの書き換えで対応します。

その他の仕様は以下の通りです。

複合ビデオ出力、Sビデオ出力、アナログRGB出力、デジタルRGB出力は同時使用可能です。 今回のポイントは、小規模のデバイスにできるだけ多くの機能を詰め込むためにライトバッファを 省略したことと、複数の表示器に対応するために、複合同期と水平、垂直同期の信号間に位相差を つけたことです。 ライトバッファは、一種のレジスタまたはFIFOで、CPUから表示用メモリへの書き込みアクセス時、 書き込みをCRTC内のライトバッファに受け付けてCPUは解放し、表示用メモリにアクセスできる タイミングになった時点でCRTCがライトバッファから表示用メモリに書き込むことでCPUを待たせる 時間を短くするもので、高速化の一般的な手法です。 しかし、単純な1段のライトバッファでも、アドレスとデータのビット数分のFFが必要なので、 今回の128個のFFしかもたないCPLDにとって無視できない回路規模です。 そこで、解像度が低いこともあり、性能低下はわずかと判断してライトバッファは省略します。 その他、書き込みデータのサンプリングをライトストローブの立下り基準で行う(立下りそのもので 行うわけではない)ことで気持ち程度の対策としています。 CPLDの記述はALTERA独自のHDLであるAHDLで行っています。 VHDLより記述量がかなり少なくなるので簡単なものを記述するには便利です。 あまり一般的ではないHDLですが、VHDLやABELが解かる人なら見ればすぐ解かると思います。 なお、座標とアドレスの対応は以下のようになります。 256色版 address(x, y) = base address + y * 512 + x (0≦y≦255, 0≦x≦511) 16色版 address(x, y, plane) = base address + 0x10000 * plane + y * 256 + x/2 (0≦y≦255, 0≦x≦511, 0≦plane≦1) 16色版では1バイトに2ドット分のデータが入り、上位4ビットが左側、下位4ビットが右側の ドットのデータです。またplaneは0が前景、1が背景で、plane0のデータ0の画素のみplane1が 透けて見えるように合成されます。 |

| 説明書(.pdf)(2004.01.13更新) |

| 回路図(.pdf)(2002.08.17更新) |

| 基板図(.pdf)(2002.08.17追加) |

| CPLDプログラム(2002.07.28更新) |

| CPLD書き込み用ケーブル回路図など(.pdf)(2002.08.17追加) |

|

2002年12月16日追記 16色版の輝度ビットの扱いを変更したバージョンを作りました。 今までのバージョンでは、 R2 = R R1 = I R0 = R G2 = G G1 = I G0 = G B2 = B B1 = I B0 = B でしたが、今回のバージョンでは、 R2 = R R1 = R and I R0 = R and I G2 = G G1 = G and I G0 = G and I B2 = B B1 = B and I B0 = B and I と変更しました。 この変更で透明色の黒(値0)と不透明色の黒(値8)ができるため見かけ上の色数は15色となります。 なお、256色版については変更ないので今回追加のファイルには含まれていません。 |

| 16色版CPLDプログラム Ver.1.01(2002.12.16追加) |

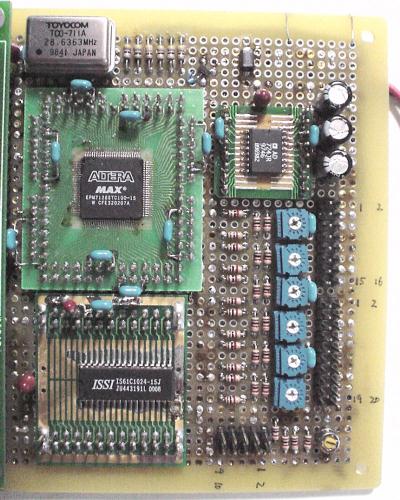

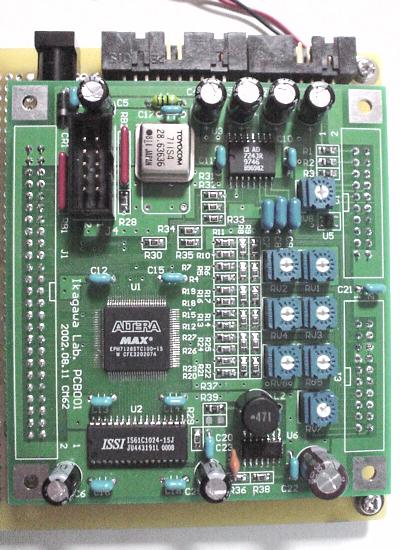

CRTC部の拡大。 |

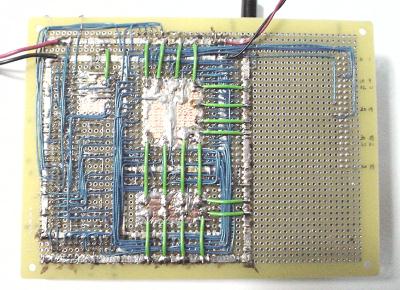

半田面の様子。青い線はラッピングワイヤと同じ径の撚線。 |

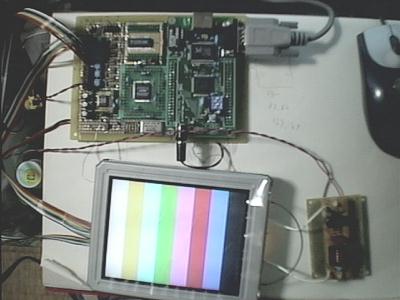

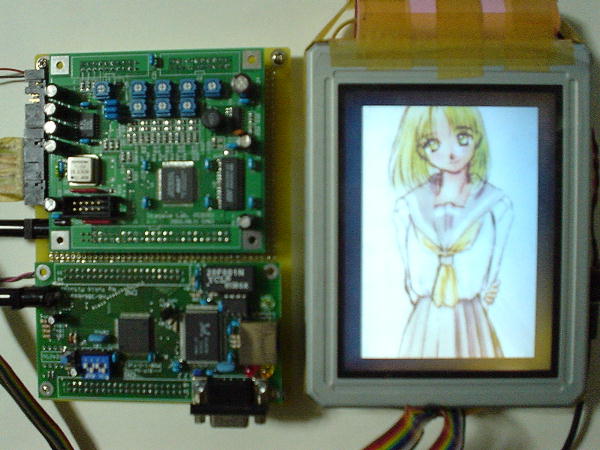

SHARP製液晶モジュールLM32C041(デジタルRGB入力)に表示した様子 |

プリント基板を作ってみました。仕事で作るのに較べると随分安くできるものですね。 |

SHARP製液晶モジュールLM32C041(デジタルRGB入力)に表示した様子。写真ボケてますね・・・ |